"Чудеса" российской электроники

Категории: Техника » Компьютеры

ЗАО "МЦСТ" и ОАО "ИНЭУМ им. И.С.Брука" демонстрируют на 9 Международной выставке "ChipExpo-2011", которая проходит в г. Москве в период с 1 по 3 ноября 2011 года в Центральном выставочном комплексе "Экспоцентр" новые процессоры, персональные компьютеры, ноутбуки и другую электронику работающую на микроэлектронике и процессорах собственного производства.

Категории и теги: Техника » Компьютеры » Эльбрус-2С, МЦСТ, Процессор, Ноутбук, ChipExpo.

Большой интерес IT-специалистов и программистов вызвал новый многоядерный микропроцессор "Эльбрус-2С+" собственной архитектуры, южный мост "КПИ" для подключения периферийных устройств со всеми современными интерфейсами, и вычислительные комплексы на их основе. Также на выставке продемонстрирован новейший 4 ядерный микропроцессор "МЦСТ R1000@ (в процессе разработки обозначался "МЦСТ-4R"), новые продукты на базе микропроцессора "R500S" архитектуры SPARC: компьютер на модуле МУП/С в конструктиве CompactPCI 3U, защищённый ноутбук и тонкий клиент.

Новый этап в разработке российских микропроцессоров - подписан Акт приемки опытно-конструкторской работы «Разработка комплекта сверхбольших интегральных схем типа “система на кристалле” для применения в системах обработки радиолокационной информации». Завершена совместная разработка микросхемы «Эльбрус-2С+» компаниями ЗАО «МЦСТ» и ГУП НПЦ «Элвис».

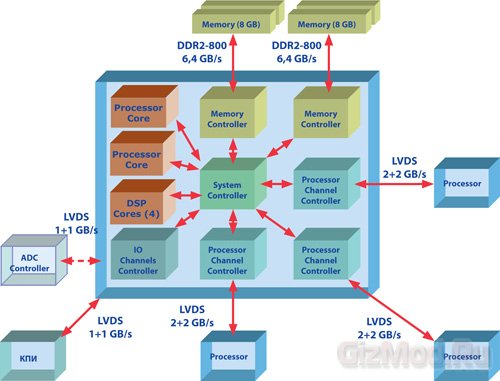

Выдержки из Акта, подписанного членами Комиссии по проведению государственных испытаний: «Разработанная микросхема интегральная 1891 ВМ7Я является импортозамещающей СБИС, обеспечивающей ввод оцифрованных высокоскоростных сигналов от антенных систем, их предварительную, первичную и вторичную цифровую обработку в режиме жесткого реального времени. В состав микросхемы входят четыре разработанных ГУП НПЦ «Элвис» специализированных процессорных ядра для быстрой предварительной обработки цифровой сигнальной информации и два разработанных ЗАО «МЦСТ» универсальных процессорных ядра для выполнения универсальных алгоритмов первичной и вторичной обработки информации. На универсальную часть микросхемы также возлагается задача управления работой всей 6-ядерной системы. Универсальное процессорное ядро микросхемы «Эльбрус-2С+» является высокопроизводительным универсальным микропроцессором с архитектурой широкого командного слова, имеет параллельную внутреннюю двухкластерную организацию. Архитектура универсального ядра включает аппаратные средства для организации защищенных вычислений, обеспечивает поддержку объектно-ориентированного программирования, содержит средства поддержки выполнения программного обеспечения платформы х86. Входящий в состав микросхемы DSP-кластер представляет собой четырехядерную мультипроцессорную систему и содержит четыре специализированных ядра для быстрой обработки цифровой сигнальной информации, работающих на на общем поле памяти данных, набор общих для всего кластера регистров управления/состояния, регистровый файл общего доступа, контроллер DMA, а также AXI-коммутатор. Операционная система обеспечивает возможность организации вычислений в режиме жесткого реального времени, аппаратно поддержанную возможность резервирования микросхем, возможность комплексирования микросхем в вычислительные системы. Сиcтема программирования, единая для универсальных ядер и средств цифровой обработки сигналов, включает оптимизирующие компиляторы языков С/C++, ориентированные на многопроцессорную и многопотоковую обработки.»

Выдержка из «Решения об утверждении Акта государственных испытаний»: «ЗАО «МЦСТ» приступить установленным порядком к выпуску серийных образцов микросхемы 1891 ВМ7Я.».

Эльбрус-2С+ - первый гибридный высокопроизводительный микропроцессор фирмы МЦСТ. Он содержит 2 ядра архитектуры Эльбрус и 4 ядра цифровых сигнальных процессоров (DSP) фирмы Элвис. Основная сфера применения процессора Эльбрус-2С+ - системы цифровой интеллектуальной обработки сигнала, такие как радары, анализаторы изображений и т.п.

По сравнению с процессором Эльбрус-S, в процессор Эльбрус-2С+ были введены следующие изменения:

Число ядер архитектуры Эльбрус увеличено до 2.

Кэш-память 2-го уровня уменьшена до 1 МБ на ядро.

Добавлен кластер из 4 ядер DSP, работающих на той же частоте.

Поддерживаемый тип памяти изменён на DDR2-800, пропускная способность улучшилась на 60%

Добавлен ещё один канал ввода-вывода. К нему можно подключить дополнительный южный мост КПИ или специализированное устройство, например контроллер ЦАП/АЦП.

Для гибридного процессора реализована версия компилятора с языка Си, позволяющая компилировать код для ядер DSP и обеспечивать эффективное взаимодействие основной программы, исполняющейся на ядрах CPU, и процедур для DSP.

Категория: Техника » Компьютеры

| 3-11-2011, 17:46 | Просмотров: 8 911 | Комментарии (1)